# ECE 205 "Electrical and Electronics Circuits"

## **Spring 2024 – LECTURE 32** MWF – 12:00pm

**Prof. Umberto Ravaioli**

2062 ECE Building

# Lecture 32 – Summary

- **Learning Objectives**

- 1. Logic gates realized physically with BJT's

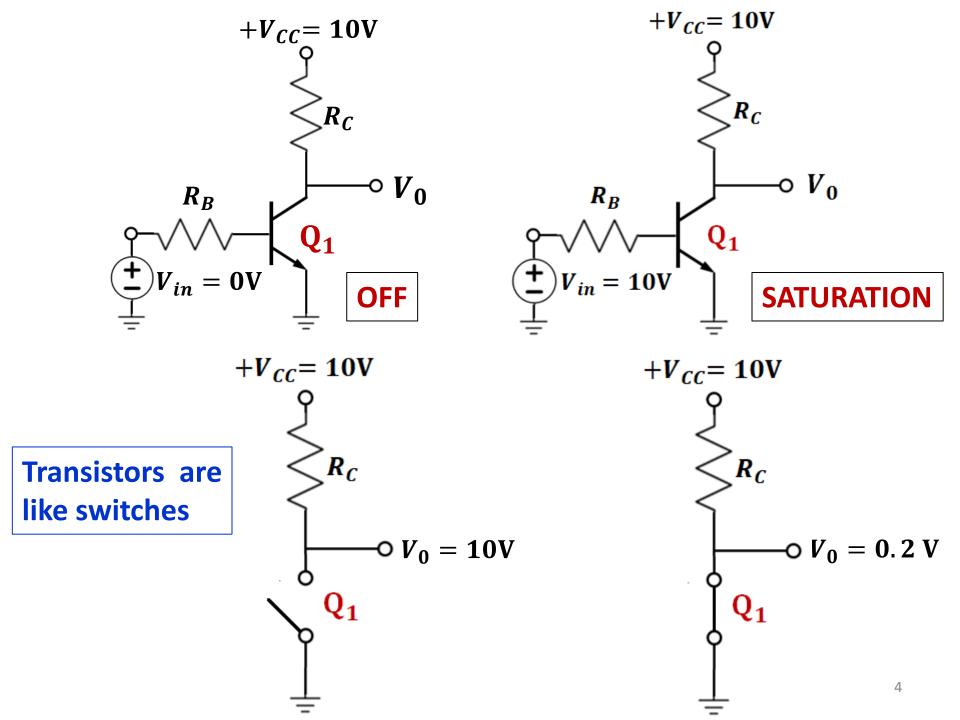

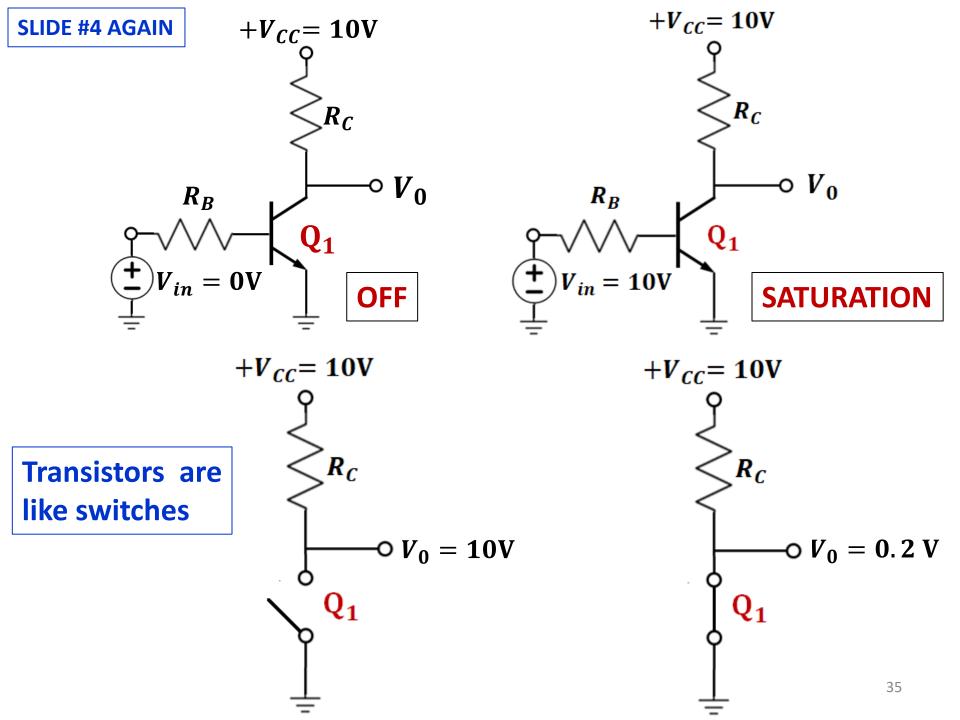

### **Basic Inverter (NOT) implementation**

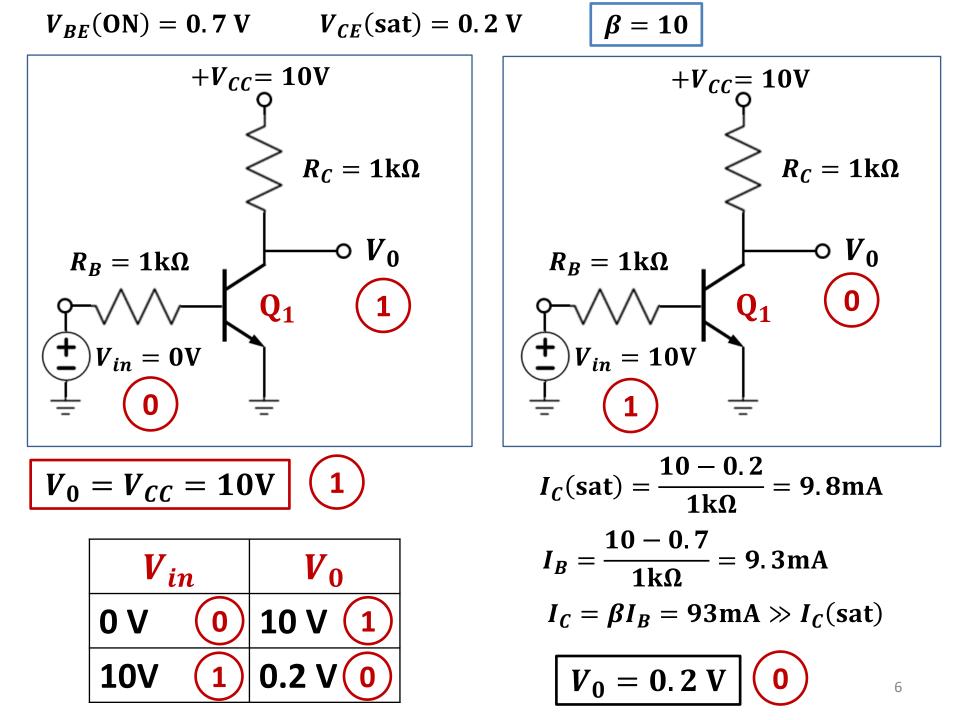

$$V_{BE}(ON) = 0.7 V$$

$V_{CE}(sat) = 0.2 V$

$$\beta = 10$$

$$+V_{CC} = 10V$$

$$R_{C} = 1k\Omega$$

$$R_{B} = 1k\Omega$$

$$Q_{1}$$

$$U_{in} = 0V$$

$$= 10V$$

$$U_{in} = 10V$$

$$V_0 = V_{CC} = 10V$$

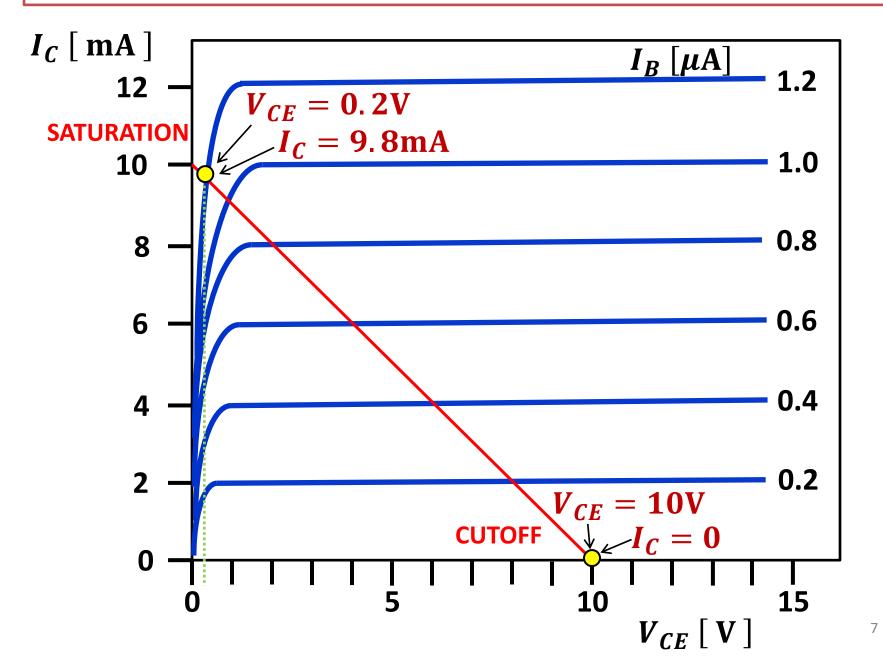

### On the *I-V* curves

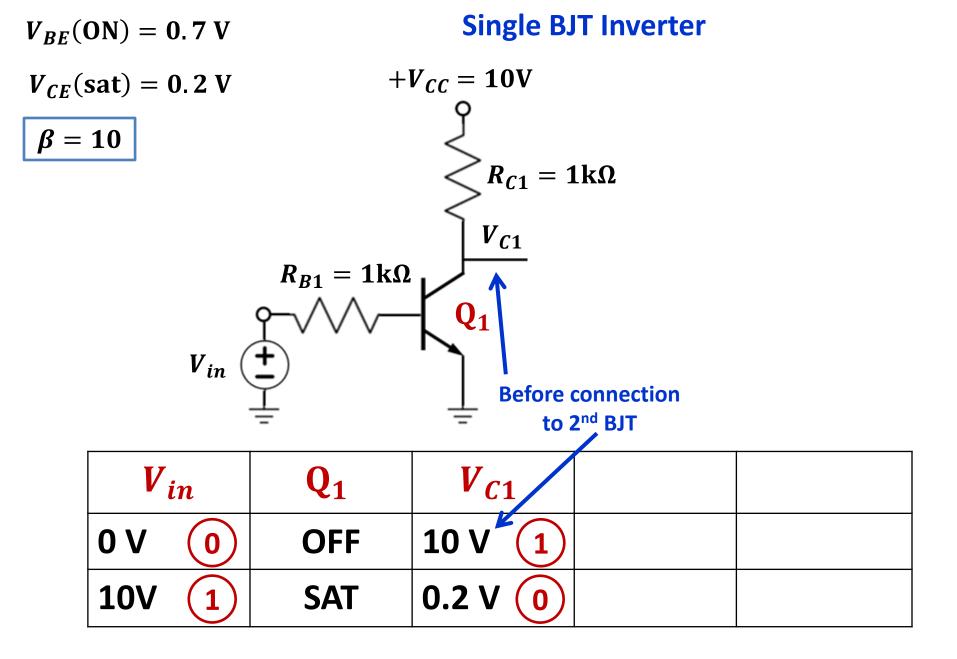

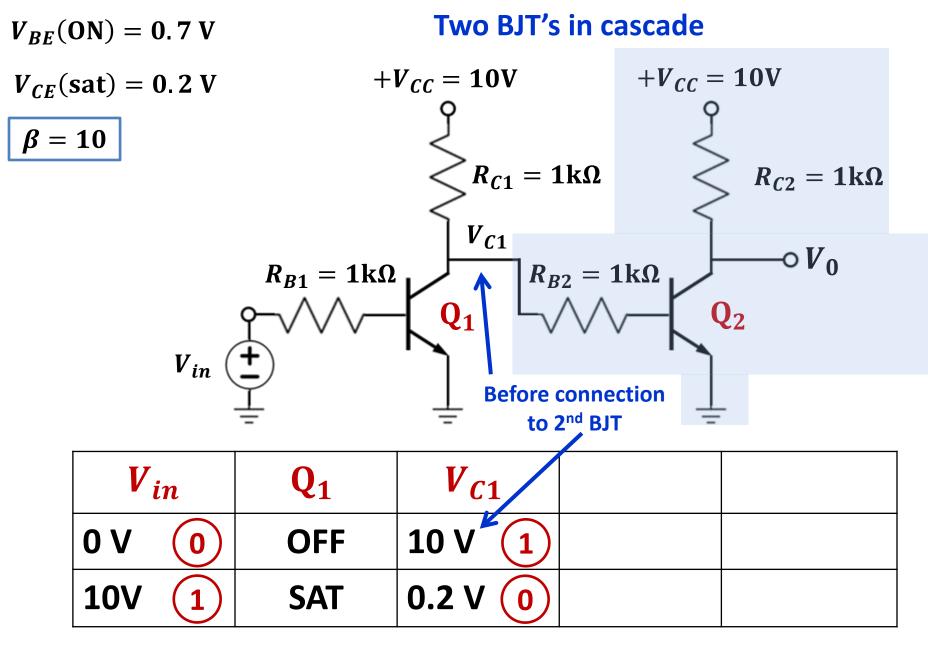

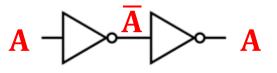

### **Two transistors in cascade**

### **Buffer implementation**

Two NOT gates in series

####

-> See next

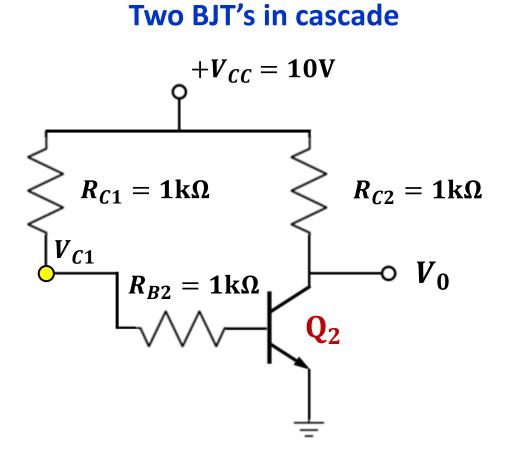

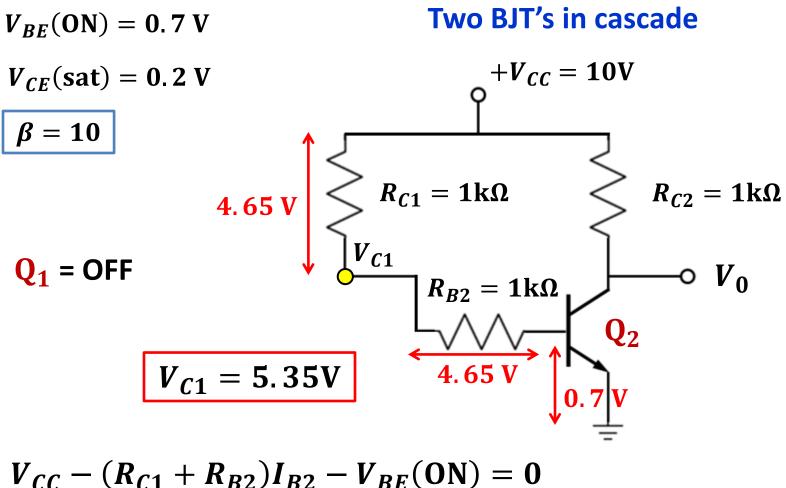

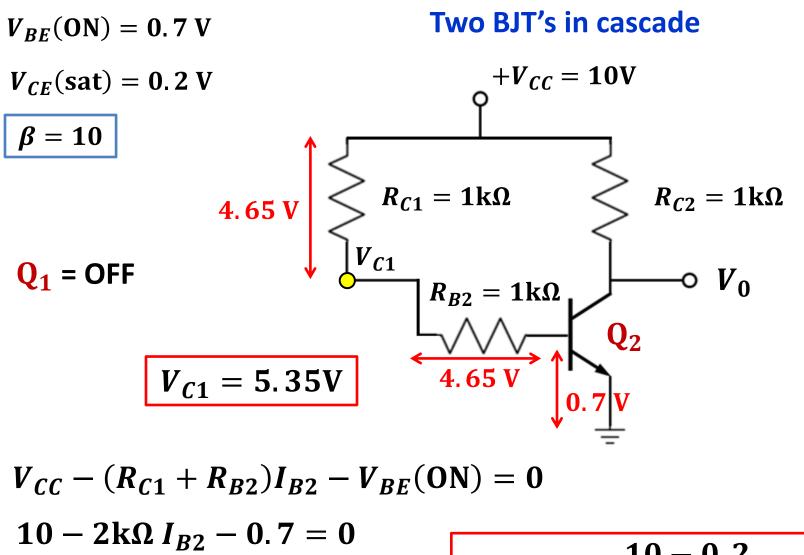

$V_{BE}(ON) = 0.7 V$  $V_{CE}(sat) = 0.2 V$  $\beta = 10$

$\mathbf{Q}_1 = \mathsf{OFF}$

$V_{CC} - (R_{C1} + R_{B2})I_{B2} - V_{BE}(ON) =$ 10 - 2k $\Omega I_{B2}$  - 0.7 = 0  $I_{B2} = 9.3/2k = 4.65mA$

Assuming forward-active mode  $I_{C2} = 46.5 \text{mA}$

$$I_{B2} = 9.3/2k = 4.65mA$$

$I_{C2}(\text{sat}) = \frac{10 - 0.2}{1\text{k}} = 9.8\text{mA}$

Assuming forward-active mode  $I_{C2} = 46.5 \text{mA}$

$$Q_2 = SATURATION$$

#### **Two BJT's in cascade** $V_{BE}(ON) = 0.7 V$ $+V_{CC} = 10V$ $+V_{CC}=10V$ $V_{CE}(\text{sat}) = 0.2 \text{ V}$ $\beta = 10$ $R_{C1} = 1 \mathrm{k} \Omega$ $R_{C2} = 1 \mathrm{k} \Omega$ $V_{C1}$ $\circ V_0$ $R_{B1} = 1 \mathrm{k} \Omega$ $R_{B2} = 1 \mathrm{k} \Omega$ $\mathbf{Q}_2$ $Q_1$ $V_{in}$ $V_{in}$ $V_{C1}$ $V_0$ $\mathbf{Q}_{\mathbf{2}}$

|     |   | ~ _ | • •      |     | <b>~</b> |

|-----|---|-----|----------|-----|----------|

| 0 V | 0 | OFF | 5.35V 1  | SAT | 0.2 V () |

| 10V | 1 | SAT | 0.2 V () | OFF | 10 V (1) |

**Two NOT gates in series**

14

### **Two transistors in cascade**

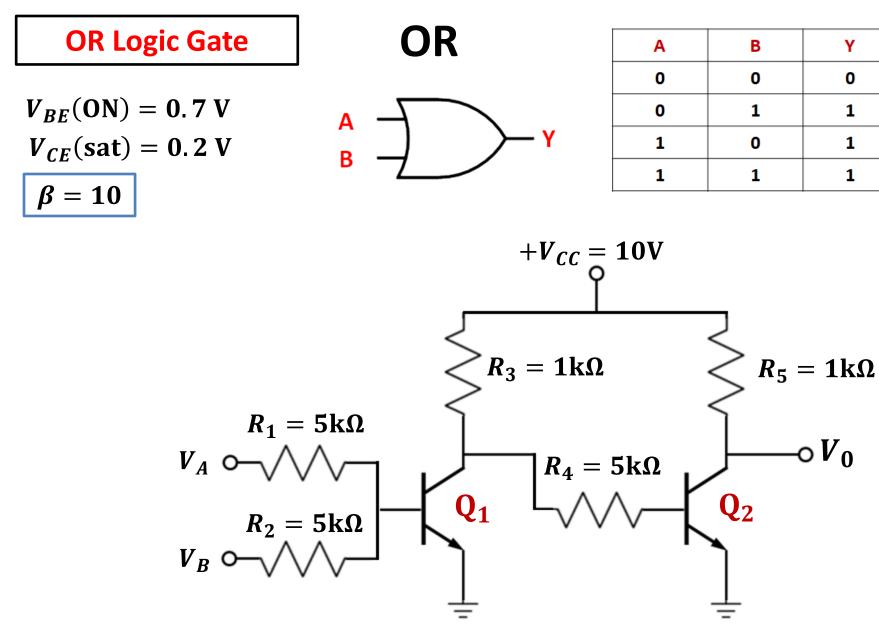

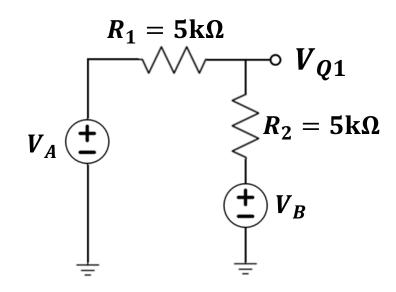

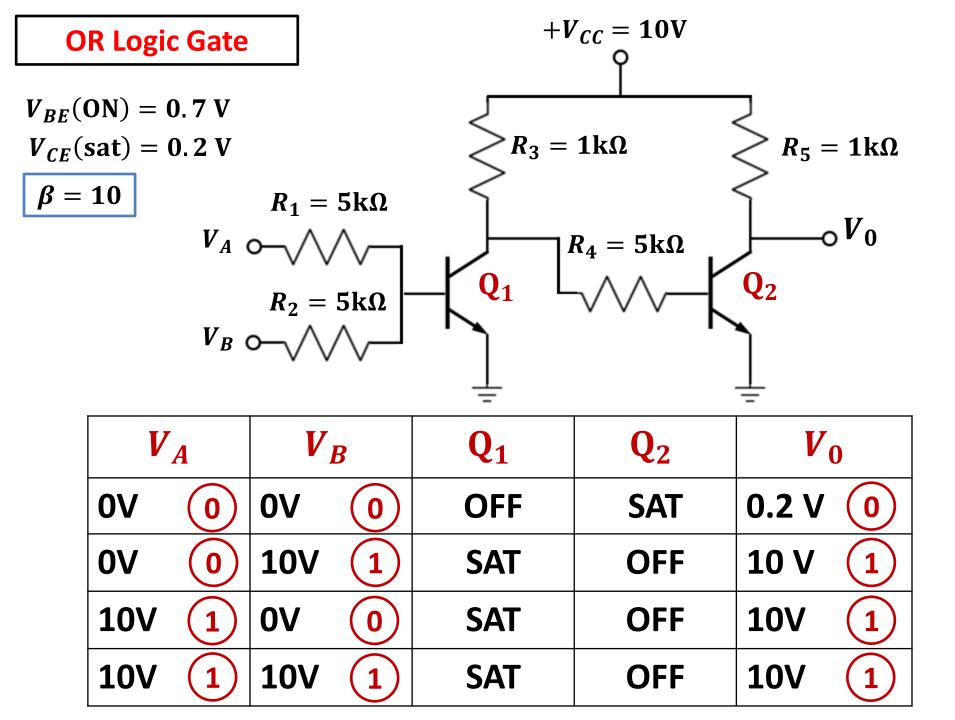

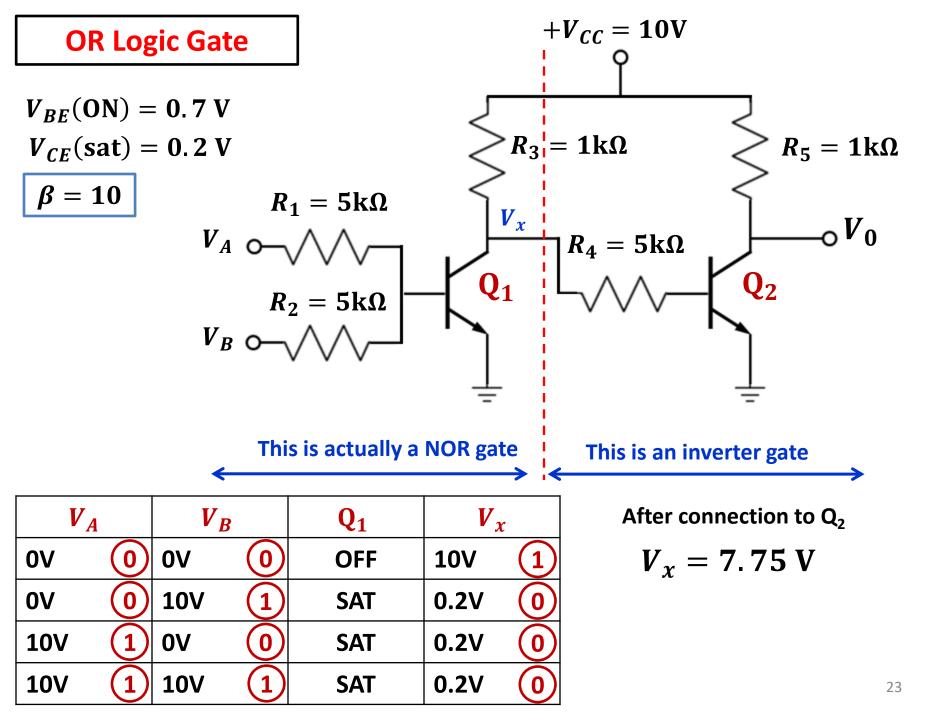

### **OR gate implementation**

Υ

$$V_{BE}(ON) = 0.7 V$$

$$V_{CE}(sat) = 0.2 V$$

$$\beta = 10$$

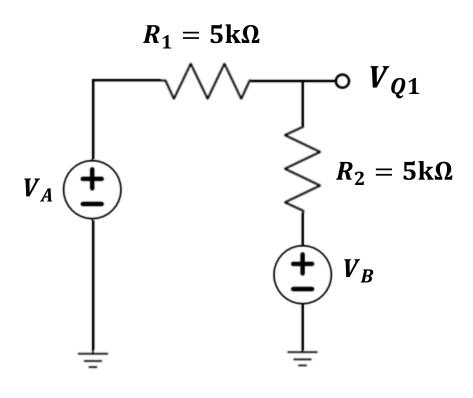

$$\frac{V_{Q1} - V_A}{5k} + \frac{V_{Q1} - V_B}{5k} = 0$$

$$V_{Q1} = \frac{V_A + V_B}{2}$$

$$V_A = 0 \qquad V_B = 0$$

$$V_{Q1} = 0$$

$$V_A = 10V \qquad V_B = 0$$

$$V_{Q1} = 5V$$

$$V_A = 0 \qquad V_B = 10V$$

$$V_{Q1} = 5V$$

$$V_A = 10V \qquad V_B = 10V$$

$$V_A = 10V \qquad V_B = 10V$$

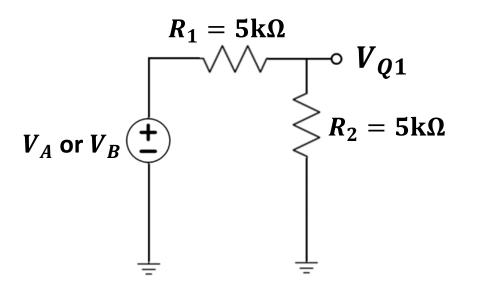

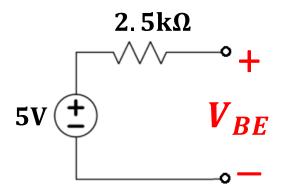

#### Thevenin Equivalent base circuit for $Q_1$

$V_{BE}(ON) = 0.7 V$  $V_{CE}(sat) = 0.2 V$  $\beta = 10$ **10V** 1kΩ •*V*<sub>1</sub>  $\mathbf{Q}_{\mathbf{1}}$ V<sub>Q1</sub>o 10 - 0.2 $I_{\mathcal{C}}(\operatorname{sat}) = -$ = 9.8mA 1kΩ

$$V_{Q1} = \mathbf{0}$$

$$V_1 = \mathbf{10} \mathbf{V}$$

$$V_{Q1} = 5V$$

$$I_{B} = \frac{5 - 0.7}{2.5 k\Omega} = 1.72 mA$$

$$I_{C} = \beta I_{B} = 17.2 mA \gg I_{C}(sat)$$

$$V_{1} = 0.2 V$$

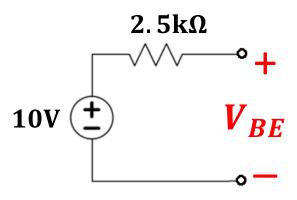

$$V_{Q1} = 10V$$

$$I_{B} = \frac{10 - 0.7}{2.5 k\Omega} = 3.72 mA$$

$$I_{C} = \beta I_{B} = 37.2 mA \gg I_{C}(sat)$$

$$V_{1} = 0.2 V$$

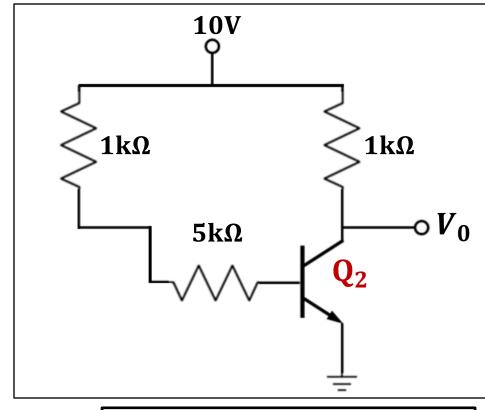

$V_{BE}(ON) = 0.7 V$  $V_{CE}(sat) = 0.2 V$  $\beta = 10$

$I_{C}(\text{sat}) = \frac{10 - 0.2}{1 \text{k}\Omega} = 9.8 \text{mA}$

$Q_1$  OFF

$$I_B = \frac{10 - 0.7}{1k\Omega + 5k\Omega} = 1.55 \text{mA}$$

$$I_C = \beta I_B = 15.5 \text{mA} \gg I_C(\text{sat})$$

$$V_0 = 0.2 V$$

$Q_2$  SATURATION

$V_{BE}(ON) = 0.7 V$  $V_{CE}(sat) = 0.2 V$  $\beta = 10$ **10V** 1kΩ  $\circ V_0$  $V_1$  $\mathbf{Q}_2$

$Q_1$  SATURATION  $V_1 = V_{CE}(sat)$  $= 0.2V < V_{BE}(ON)$  $I_B = 0$  $I_C = 0$  $V_0 = 10 V$  $\mathbf{Q}_2$  OFF

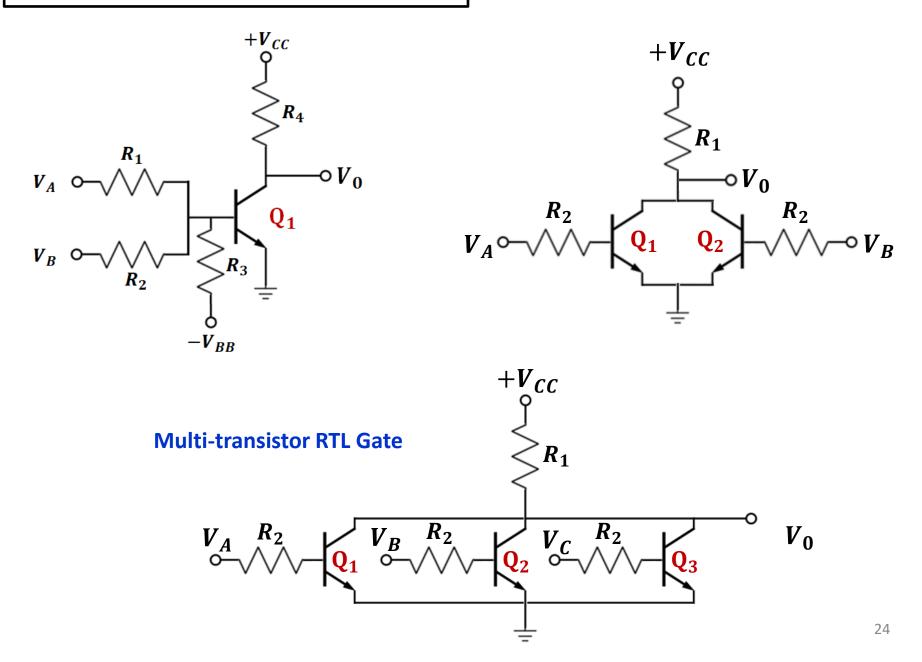

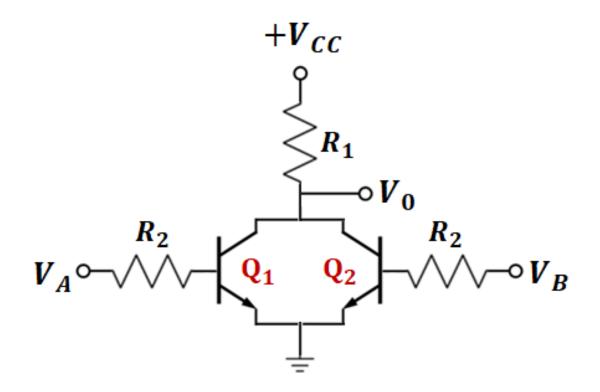

#### **Other NOR implementations**

#### NOR

$$V_{CC} = 10V$$

| V <sub>A</sub> | V <sub>B</sub> | <b>Q</b> <sub>1</sub> | <b>Q</b> <sub>2</sub> | V <sub>0</sub> |

|----------------|----------------|-----------------------|-----------------------|----------------|

| 0V ()          | 0V <b>()</b>   | OFF                   | OFF                   | 10 V 1         |

| 0V ()          | 10V (1)        | OFF                   | SAT                   | 0.2 V ()       |

| 10V 1          | 0V <b>()</b>   | SAT                   | OFF                   | 0.2 V ()       |

| 10V 1          | 10V (1)        | SAT                   | SAT                   | 0.2 V ()       |

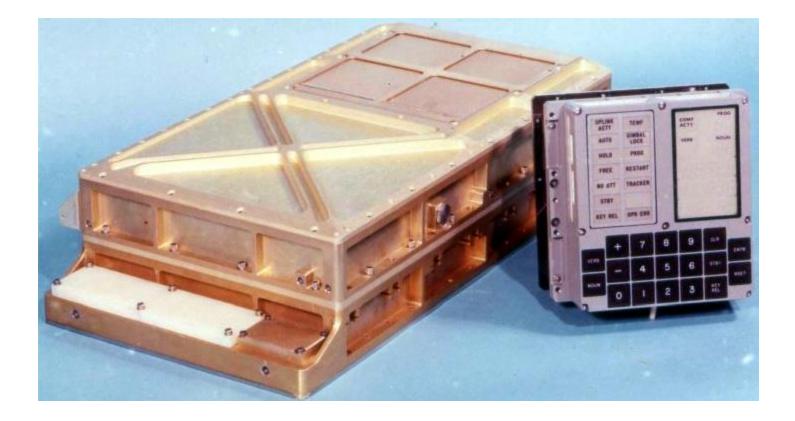

RTL-based NOR circuits were used in the Apollo Guidance Computer that went to the moon (the first computer using silicon integrated circuits)

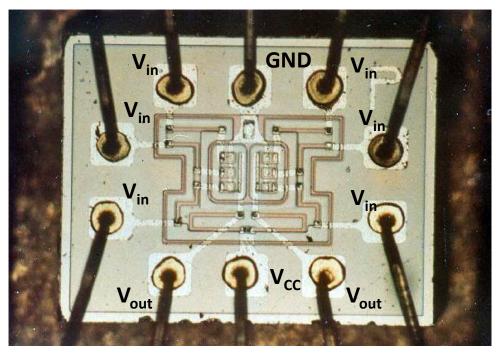

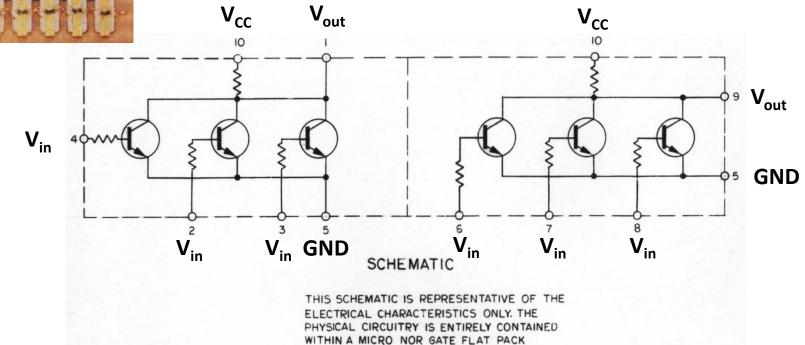

Silicon integrated circuit with two 3-inputs NOR gates, used in the Apollo Guidance computer.

computerhistory.org/blog/silicon-chips-take-man-to-the-moon/

321

527

27

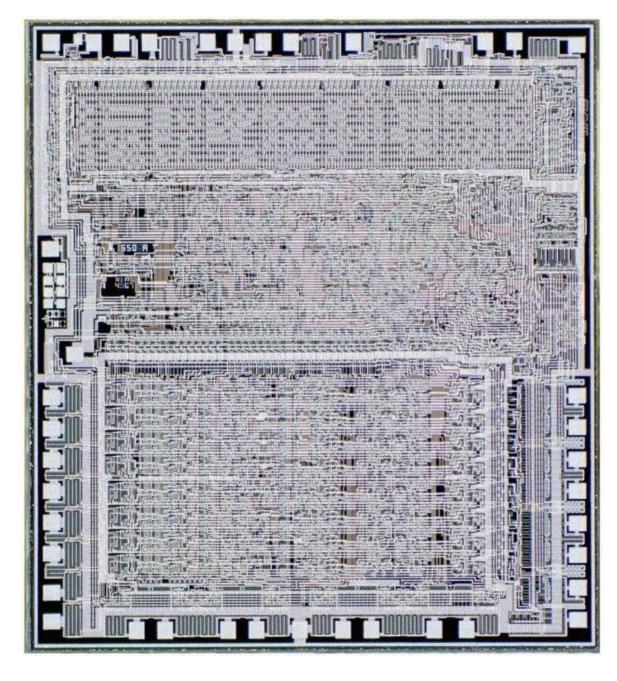

MOS Technology 6502 8-bit microprocessor (1975) 3510 transistors (MOSFET)

#### CPU of:

- Apple II

- Atari 400 & 800

- BBC Micro

- Commodore PET & VIC-20

#### Photo: © Antoine Bercovici

Semiconductor chips in consumer products have now billions of transistors

Apple M2 Max has 67 billion MOSFETs (2023) Apple M2 Ultra (2×M2 Max) has 134 billion MOSFETs

AMD's MI300X has 153 billion MOSFETs (2023)

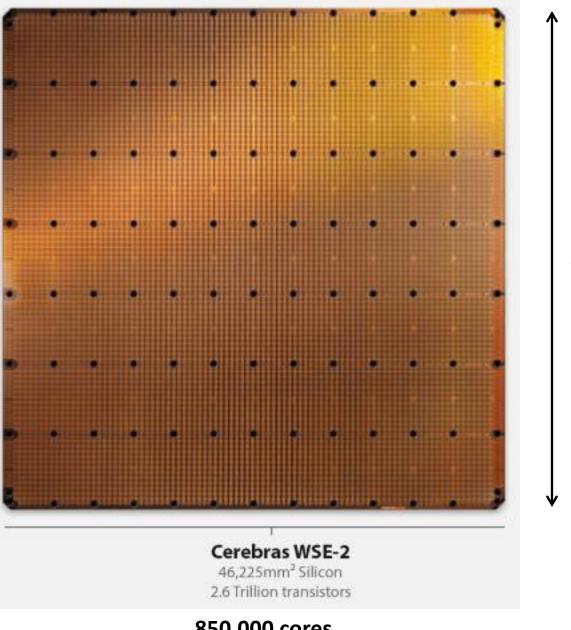

The Wafer Scale Engine 2 (WS2) deep-learning processor by Cerebras has 2.6 trillion MOSFETs

#### 850,000 cores Memory bandwidth = 20 Petabytes/sec

https://www.cerebras.net/product-chip/

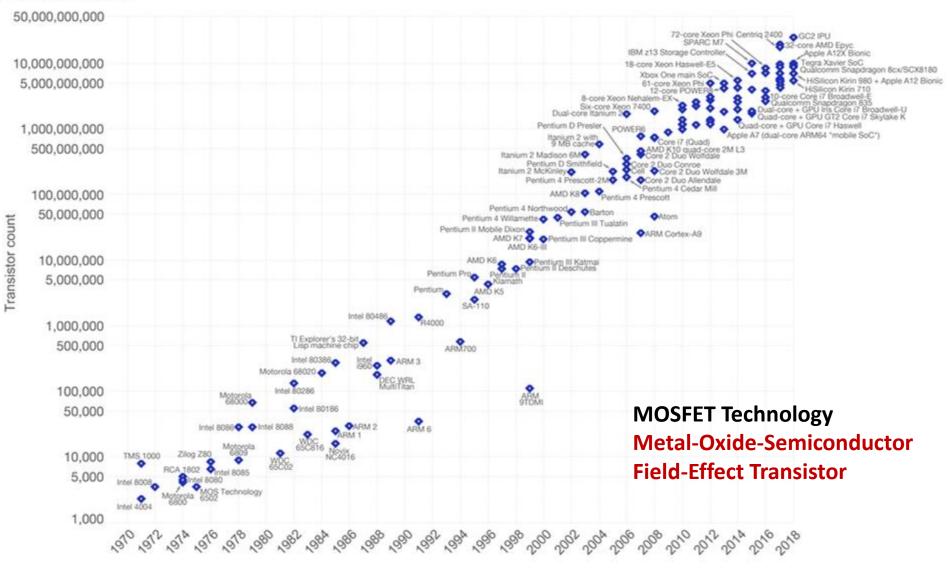

#### Moore's Law - The number of transistors on integrated circuit chips (1971-2018)

Our World in Data

Moore's law describes the empirical regularity that the number of transistors on integrated circuits doubles approximately every two years. This advancement is important as other aspects of technological progress – such as processing speed or the price of electronic products – are linked to Moore's law.

• Estimated number of grains of sand on Earth

$\approx 7.5 \times 10^{18}$  (seven quintillion five hundred quadrillions grains)

• Estimated number of transistors fabricated since 1947  $\approx 2.9 \times 10^{21}$  (2.0 sextillion transistors) [2014]  $\approx 1.3 \times 10^{22}$  (13 sextillion transistors) [2022]

- Estimated number of stars in the Universe visible with the Hubble telescope (2003)

- Estimated number of H<sub>20</sub> molecules in 10 drops of water

- $\approx 7.0 \times 10^{22}$  (70 sextillions)

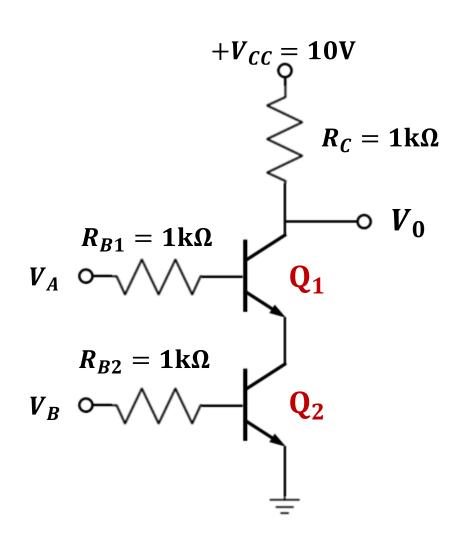

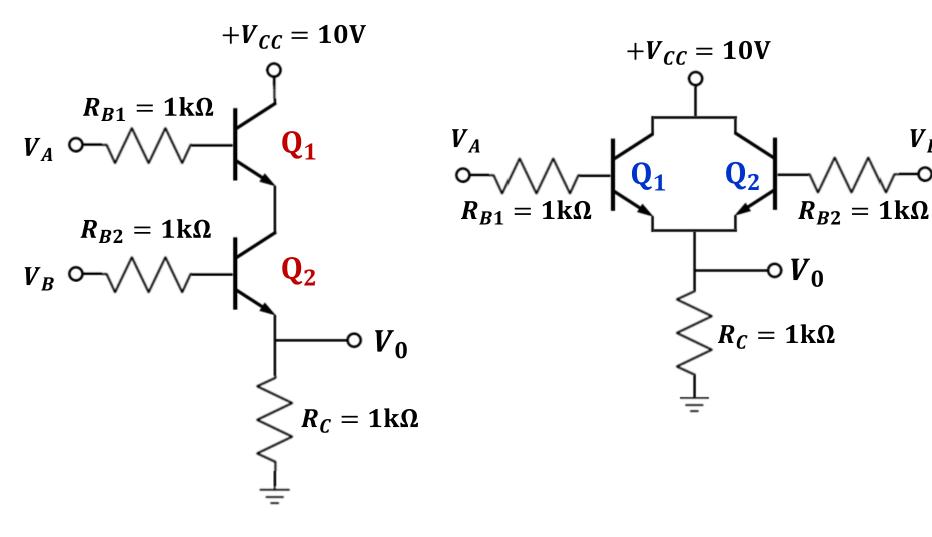

### **Two transistors in series**

### **NAND** gate implementation

**Two transistors in series**

$V_{BE}(ON) = 0.7 V$  $V_{CE}(sat) = 0.2 V$  $\beta = 10$

#### **Two transistors in series**

$V_{BE}(ON) = 0.7 V$  $V_{CE}(sat) = 0.2 V$

$$\beta = 10$$

$$V_{A} = V_{B} = 0V$$

$$V_{A} = 10V$$

$$V_{A} = 10V$$

$$V_{B} = 10V$$

$$V_{B} = 0V$$

$$V_{A} = V_{B} = 10V$$

$$V_{A} = 0$$

$$V_{A} =$$

| Ти                                                      | vo transistor  | s in series                                                                                         |                            | +                                                                   | $V_{cc} = 10V$ |

|---------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------|----------------|

| $V_{BE}(ON) = 0.7 V$ $V_{CE}(sat) = 0.2 V$ $\beta = 10$ |                | NAND<br>A Y                                                                                         |                            | $R_{B1} = 1k\Omega$ $V_{A} \circ V_{0}$ $Q_{1}$ $R_{B1} = 1k\Omega$ |                |

|                                                         |                | A         B           0         0           0         1           1         0           1         1 | Y<br>1<br>1<br>1<br>1<br>0 | $R_{B2} = 1 k\Omega$                                                |                |

|                                                         | V <sub>A</sub> | V <sub>B</sub>                                                                                      | <b>Q</b> <sub>1</sub>      | <b>Q</b> <sub>2</sub>                                               | V <sub>0</sub> |

|                                                         | 0V ()          | 0V ()                                                                                               | OFF                        | OFF                                                                 | 10 V 1         |

|                                                         | 0V ()          | 10V 1                                                                                               | OFF                        | SAT                                                                 | 10 V 1         |

|                                                         | 10V 1          | 0V ()                                                                                               | OFF                        | OFF                                                                 | 10V <b>1</b>   |

|                                                         | 10V (1)        | 10V (1)                                                                                             | SAT                        | SAT                                                                 | 0.4V ()        |

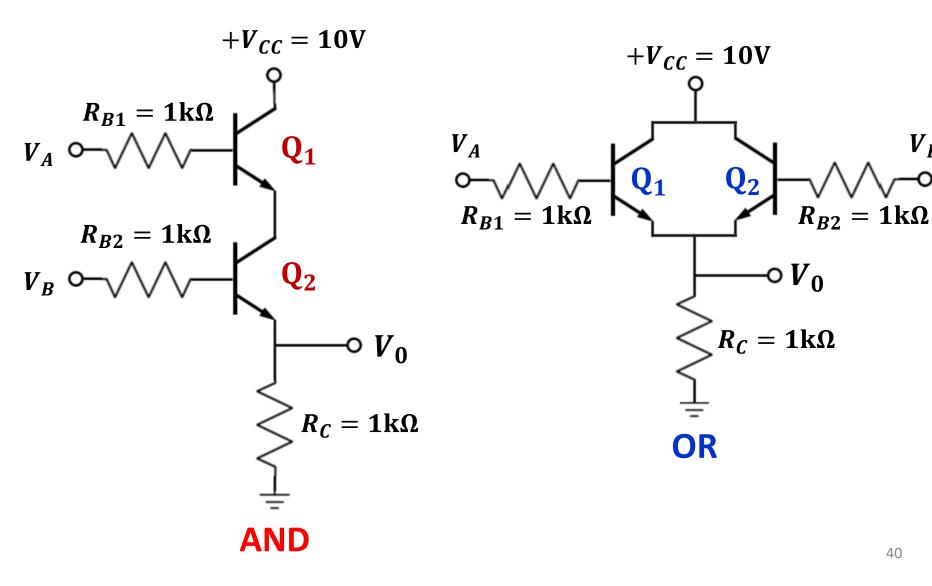

Alternative circuits – What logic gates are these?

$$V_{BE}(ON) = 0.7 V$$

$V_{CE}(sat) = 0.2 V$   $\beta = 10$

$V_B$

Alternative circuits – What logic gates are these?

$$V_{BE}(ON) = 0.7 V$$

$V_{CE}(sat) = 0.2 V$   $\beta = 10$

$V_B$

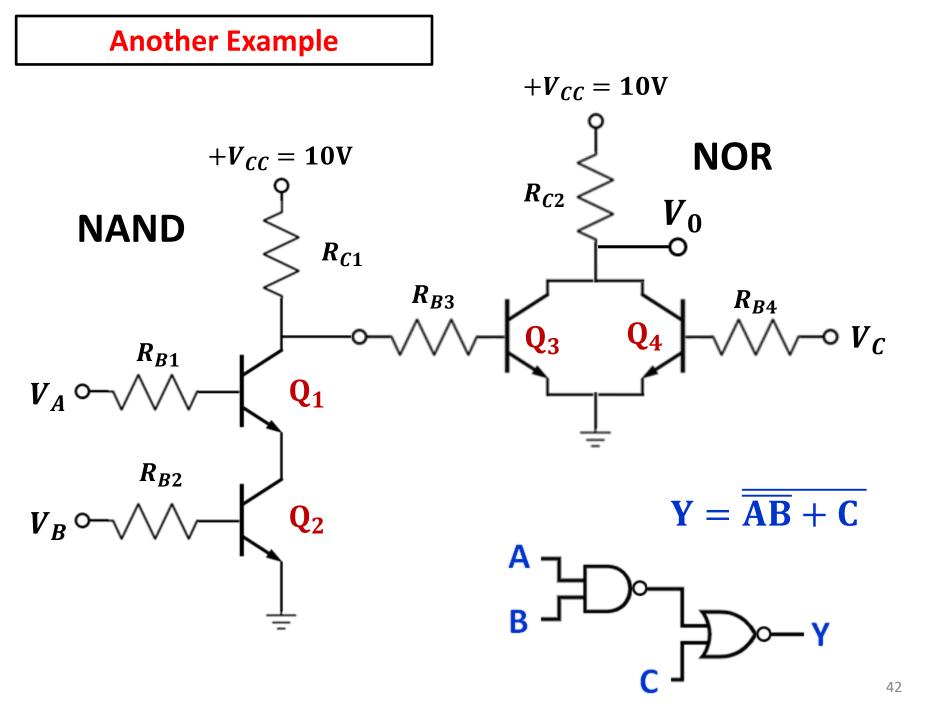

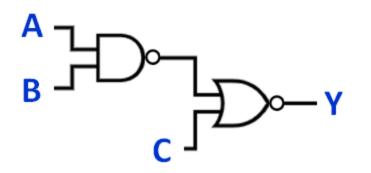

$-\mathbf{Y} \qquad \mathbf{Y} = \overline{\mathbf{AB}} + \mathbf{C}$

| Α | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

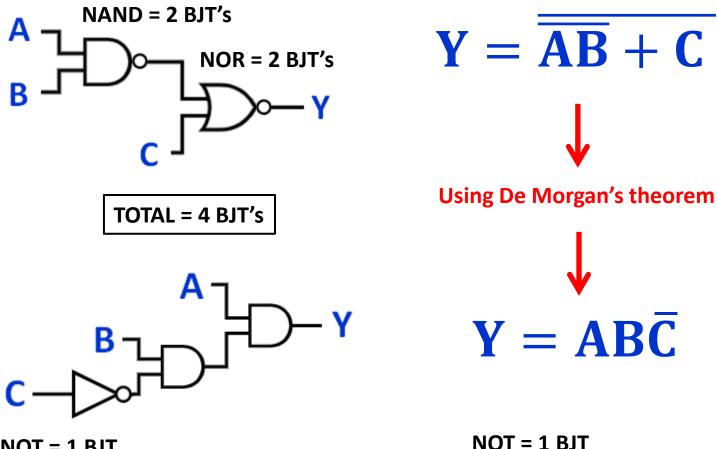

#### What if we transform the circuit?

NOT = 1 BJT Two 2-inputs NAND's = 4 BJT's

Two NOT's to obtain AND's = 2 BJT

TOTAL = 7 BJT's

NOT = 1 BJT One 3-inputs NAND = 3 BJT's NOT to obtain AND = 1 BJT